# CMOS IMAGE SENSORS DYNAMIC RANGE AND SNR ENHANCEMENT VIA STATISTICAL SIGNAL PROCESSING

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Xinqiao Liu

June 2002

© Copyright by Xinqiao Liu 2002

All Rights Reserved

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Abbas El Gamal (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Mark A. Horowitz

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Brian A. Wandell

Approved for the University Committee on Graduate Studies:

## **Abstract**

Most of today's video and digital cameras use CCD image sensors, where the electric charge collected by the photodetector array during exposure time is serially shifted out of the sensor chip resulting in slow readout speed and high power consumption. Recently developed CMOS image sensors, by comparison, are read out non-destructively and in a manner similar to a digital memory and can thus be operated at very high frame rates. A CMOS image sensor can also be integrated with other camera functions on the same chip ultimately leading to a single-chip digital camera with very compact size, low power consumption and additional functionality. CMOS image sensors, however, generally suffer from lower dynamic range than CCDs due to their high read noise and non-uniformity. Moreover, as sensor design follows CMOS technology scaling, well capacity will continue to decrease, eventually resulting in unacceptably low SNR.

In this dissertation, new pixel architectures and algorithms are presented that enhance the dynamic range and SNR of CMOS image sensors by utilizing their high speed readout and integration advantages. The thesis is divided into three parts. First, a  $352 \times 288$  Digital Pixel Sensor (DPS) chip with per-pixel single-slope ADC and dynamic memory fabricated in a standard digital  $0.18\mu m$  CMOS process is presented that demonstrates the high speed potential and scaling advantage of CMOS image sensors. The chip performs "snap-shot" image acquisition at continuous rate of 10,000 frames/s or 1 Gpixels/s. Second, an algorithm based on statistical signal processing techniques is presented that synthesizes a high dynamic range, motion blur free, still image or video sequence from multiple image captures. The algorithm

is recursive and consists of two main procedures – photocurrent estimation and motion/saturation detection. Photocurrent estimation is used to reduce read noise and thus to enhance dynamic range at the low illumination end. Saturation detection is used to enhance dynamic range at the high illumination end, while motion blur detection ensures that the estimation is not corrupted by motion. Motion blur detection also makes it possible to extend exposure time and to capture more images, which can be used to further enhance dynamic range at the low illumination end. The algorithm operates completely locally and recursively, its modest computation and storage requirements make the algorithm well suited for single chip digital camera implementation. Finally, to solve the problem with CMOS technology scaling and further enhance sensor SNR at high illumination, a self-resetting scheme is presented. In this scheme, each pixel resets itself one or more times during exposure time as a function of its illumination level, resulting in higher effective well capacity and thus higher SNR. The photocurrent estimation algorithm is then extended to take new noise components into consideration, and simulations results demonstrate significant dynamic range and SNR improvements.

# Acknowledgments

I am deeply indebted to many people who made my Stanford years an enlightening, rewarding and memorable experience.

First and foremost, I would like to thank professor Abbas El Gamal for having accepted me into his research group. His continuing support and invaluable guidance were an inspiration during my Ph.D studies at Stanford. I have benefited from his vast technical expertise and insight, as well as his high standards in research and publication.

I am grateful to my associate advisor professor Mark Horowitz, for his support in this research, serving on my orals committee and reading my dissertation. I am also grateful to professor Brian Wandell for his support and help throughout this PDC program. It was a great pleasure working with him.

I want to thank professor Gordon Kino. It is a great honor to have him as my oral chair. I also want to thank professor Yoshihisa Yamamoto, professor John Gill, professor Leonard Tyler, professor Joseph Goodman, and professor Peter Glynn for their help and guidance.

I gratefully appreciate the support and encouragement from Dr. Boyd Fowler, Dr. David Yang, Dr. Michael Godfrey and Dr. Hao Min. Boyd deserves special recognition.

I gratefully acknowledge Dr. Hui Tian, Dr. Stuart Kleinfelder, Sukhwan Lim, Ting Chen, Khaled Salama, Helmy Eltoukhy and Ali Ercan for their collaboration and working as officemates, along with Hossein Kakavand, Sam Kavusi and Sina Zahedi. They made our office an enjoyable environment to be working in. I would

also like to thank all the people in the PDC program for their cooperation, and all my friends for their encouragements and generous help.

I thank all the administrative associates in ISL for their kind assistance and cheerful spirit.

The programmable digital camera project is sponsored by Canon, Kodak, Hewlett-Packard, Agilent and Interval Research. I would like to thank all the companies for their support.

I am deeply indebted to our families. Without their love, I could not have reached today. Especially, I would like to thank my wife, Min, for her unconditional support and encouragement. This thesis is dedicated to her.

# Contents

| A            | Abstract |                                                   |    |

|--------------|----------|---------------------------------------------------|----|

| $\mathbf{A}$ | ckno     | wledgments                                        | vi |

| 1            | Inti     | $\operatorname{roduction}$                        | 1  |

|              | 1.1      | Solid State Image Sensors                         | 3  |

|              |          | 1.1.1 CCD Image Sensors                           | 4  |

|              |          | 1.1.2 CMOS Image Sensors                          | 7  |

|              | 1.2      | SNR and Dynamic Range Enhancement                 | 12 |

|              |          | 1.2.1 SNR and Dynamic Range                       | 12 |

|              |          | 1.2.2 Review of Dynamic Range Enhancement Schemes | 15 |

|              | 1.3      | Organization                                      | 17 |

| 2            | A 1      | 0,000 Frames/s Digital Pixel Sensor               | 19 |

|              | 2.1      | DPS Chip Overview                                 | 20 |

|              | 2.2      | Pixel Design                                      | 24 |

|              | 2.3      | Sensor operation                                  | 28 |

|              |          | 2.3.1 A/D conversion operation                    | 28 |

|              |          | 2.3.2 Imaging modes                               |    |

|              | 2.4      |                                                   | 32 |

|   |     | 2.4.1   | Electrical and optical characterization results  | 33 |

|---|-----|---------|--------------------------------------------------|----|

|   |     | 2.4.2   | Temporal Noise and FPN                           | 36 |

|   |     | 2.4.3   | Digital noise coupling                           | 37 |

|   |     | 2.4.4   | Sample images                                    | 39 |

|   | 2.5 | Summ    | nary                                             | 41 |

| 3 | Pho | otocuri | rent Estimation Algorithms                       | 43 |

|   | 3.1 | Estim   | ation Algorithms                                 | 45 |

|   |     | 3.1.1   | Estimation Ignoring Reset Noise and FPN          | 47 |

|   |     | 3.1.2   | Estimation Considering Reset noise and FPN       | 50 |

|   |     | 3.1.3   | Recursive Algorithm                              | 51 |

|   | 3.2 | Simula  | ation Results                                    | 54 |

|   | 3.3 | Summ    | nary                                             | 58 |

| 4 | Mo  | an/S    | aturation Detection Algorithms                   | 59 |

|   | 4.1 | Motio   | n/Saturation Detection                           | 62 |

|   |     | 4.1.1   | Decision rules                                   | 66 |

|   |     | 4.1.2   | Trade-off between SNR and motion blur distortion | 68 |

|   | 4.2 | Exper   | imental results                                  | 69 |

|   |     | 4.2.1   | Experimental High Speed CMOS Image Sensor System | 70 |

|   |     | 4.2.2   | Image Synthesis from Multiple Captures           | 70 |

|   | 4.3 | Summ    | nary                                             | 76 |

| 5 | AS  | elf-Re  | set Digital Pixel Sensor                         | 77 |

| • | 5.1 |         | luction                                          | 77 |

|   | 5.2 |         | eset Digital Pixel Sensor                        | 80 |

|   | 5.3 |         | current estimation algorithm                     | 83 |

|   | 5.4 |         | nary                                             | 91 |

|   |     |         |                                                  |    |

| 6            | Conclusion                         | 92  |

|--------------|------------------------------------|-----|

|              | 6.1 Summary                        | 92  |

|              | 6.2 Recommendation for future work | 93  |

| $\mathbf{A}$ | Recursive solution                 | 96  |

| В            | Weighted CDS                       | 101 |

| $\mathbf{C}$ | Non-recursive solution             | 103 |

| D            | Recursive condition                | 106 |

| ${f E}$      | Suboptimal recursive solution      | 109 |

| $\mathbf{F}$ | Prediction error                   | 113 |

| Ri           | bliography                         | 114 |

# List of Tables

| 2.1 | Chip characteristics                                             | 22 |

|-----|------------------------------------------------------------------|----|

| 2.2 | DPS chip characterization summary. All numbers, except for power |    |

|     | consumption are at 1000 frames/s                                 | 33 |

# List of Figures

| 1.1  | A typical digital camera system                                                              | 2  |  |

|------|----------------------------------------------------------------------------------------------|----|--|

| 1.2  | Photocurrent generation in a reverse biased photodiode                                       | 4  |  |

| 1.3  | 3 Block diagram of a typical interline transfer CCD image sensors                            |    |  |

| 1.4  | Potential wells and timing diagram during the transfer of charge in a                        |    |  |

|      | three-phase CCD $$                                                                           | 6  |  |

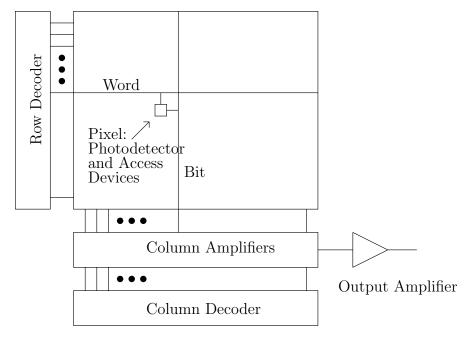

| 1.5  | Block diagram of a CMOS image sensors                                                        | 8  |  |

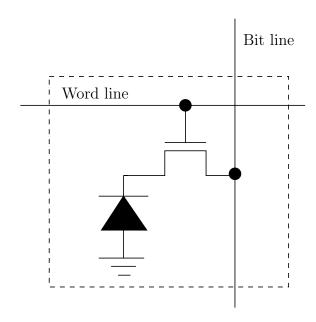

| 1.6  | Passive pixel sensor (PPS)                                                                   | 9  |  |

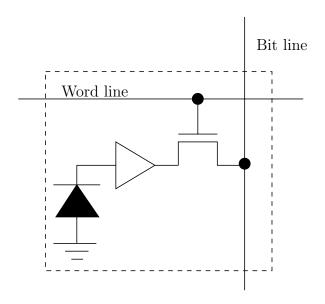

| 1.7  | Active Pixel Sensor (APS)                                                                    | 9  |  |

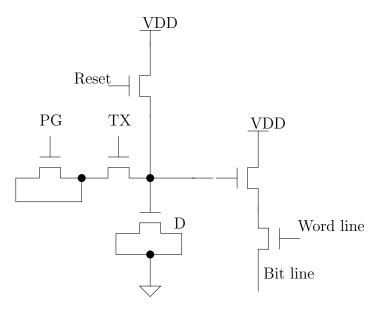

| 1.8  | Photogate APS                                                                                | 10 |  |

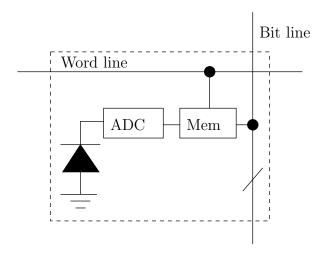

| 1.9  | Digital Pixel Sensor (DPS)                                                                   | 11 |  |

| 1.10 | CMOS image sensor pixel model                                                                | 12 |  |

| 1.11 | SNR and dynamic range for a typical sensor with well capacity, $Q_{well} =$                  |    |  |

|      | $18,750e^-$ , readout noise, $\sigma_V = 60e^-$ , reset nois, $\sigma_C = 62e^-$ , and total |    |  |

|      | integration time, $T = 32$ ms                                                                | 14 |  |

| 2.1  | Simple DPS pixel block diagram                                                               | 20 |  |

| 2.2  | DPS Chip photomicrograph. The chip size is $5 \times 5$ mm                                   | 21 |  |

| 2.3  | DPS block diagram                                                                            | 23 |  |

| 2.4  | Pixel schematic                                                                              | 25 |  |

| 2.5  | Comparator gain-bandwidth product vs. input voltage                                          |    |  |

| 2.6  | DPS pixel layout (2 × 2 pixel block shown). Pixel size is $9.4 \times 9.4 \mu m$ .           | 27 |  |

| 2.7  | Single-slope ADC operation                                                                   | 28 |  |

| 2.8  | Simplified DPS timing diagram                                             | 30 |  |

|------|---------------------------------------------------------------------------|----|--|

| 2.9  | Comparator bias generation with power-down                                | 30 |  |

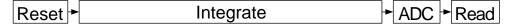

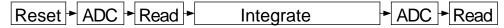

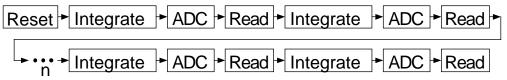

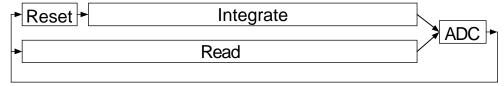

| 2.10 | Basic DPS operation schemes                                               | 31 |  |

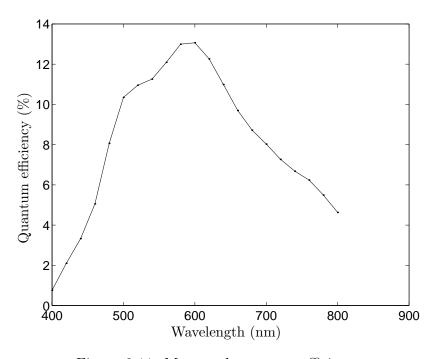

| 2.11 | Measured quantum efficiency                                               | 34 |  |

| 2.12 | Measured photogate leakage current as a function of gate voltage          | 35 |  |

| 2.13 | 8 Normalized gain versus TX bias voltage                                  |    |  |

| 2.14 | Images of fixed pattern noise without digital CDS (left) and with digital |    |  |

|      | CDS (right) for an integration time of 1ms                                | 36 |  |

| 2.15 | Images of temporal noise without digital CDS (left) and with digital      |    |  |

|      | CDS (right)                                                               | 37 |  |

| 2.16 | Digital read-induced noise experiment                                     | 38 |  |

| 2.17 | Plot of digital noise coupling results                                    | 39 |  |

| 2.18 | Sample image                                                              | 40 |  |

| 2.19 | 10,000 frames/s image sequence (frames 1, 10, 20, and 30 are shown).      | 41 |  |

| 3.1  | Simplified photodiode pixel model and the photocharge $Q(t)$ vs. time     |    |  |

|      | t under different light intensity                                         | 44 |  |

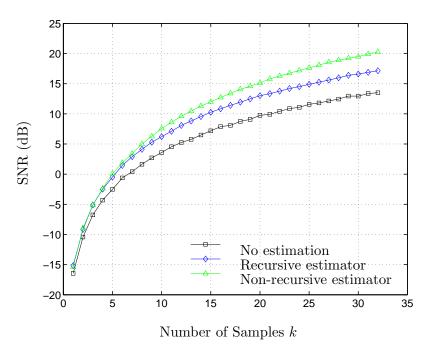

| 3.2  | Estimation weights used in the non-recursive and recursive algorithms.    | 55 |  |

| 3.3  | Equivalent Readout noise rms value vs. $k$                                | 56 |  |

| 3.4  | SNR vs. $k$                                                               | 56 |  |

| 3.5  | Estimation enhances the SNR and dynamic range                             | 57 |  |

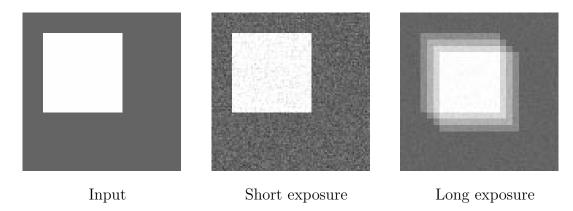

| 4.1  | Examples of images captured with short and long exposure times. The       |    |  |

|      | scene consists of a bright square object moves diagonally across a dark   |    |  |

|      | background. Short exposure results in the noisy image while long ex-      |    |  |

|      | posure results in significant motion blur                                 | 60 |  |

| 4.2  | Example of multiple captures within one exposure time                     | 60 |  |

| 4.3  | Example of high dynamic range image reconstructed using Last-Sample-      |    |  |

|      | Before-Saturation synthesis scheme                                        | 61 |  |

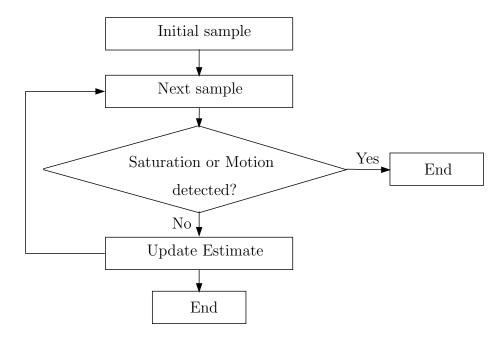

| 4.4  | Recursive photocurrent estimation from multiple captures                  | 62 |  |

| 4.5  | High dynamic range motion blur free synthesis from multiple captures.     | 63 |  |

| 4.6  | Q(t) vs. $t$ for three lighting conditions                                | 65 |  |

| 4.7  | Image produced using our algorithm with the same scene as in Figure 4.1                 | 66 |

|------|-----------------------------------------------------------------------------------------|----|

| 4.8  | Soft-decision Motion Detection                                                          | 68 |

| 4.9  | Optimal integration time under motion                                                   | 69 |

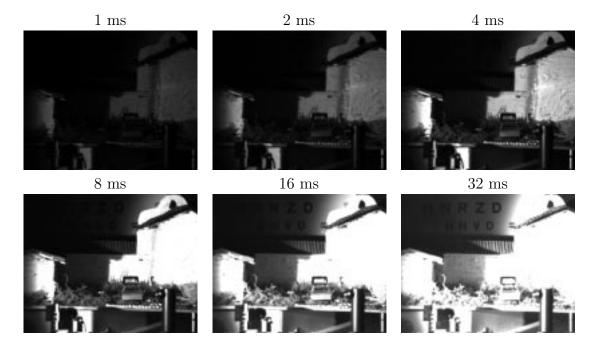

| 4.10 | Six of the 65 images of the high dynamic scene captured non-destructively               |    |

|      | at 1,000 frames/s                                                                       | 71 |

| 4.11 | High dynamic range image synthesized using the Last Sample Before                       |    |

|      | Saturation algorithm                                                                    | 72 |

| 4.12 | The high dynamic range, motion blur free image synthesized from the                     |    |

|      | 65 images                                                                               | 73 |

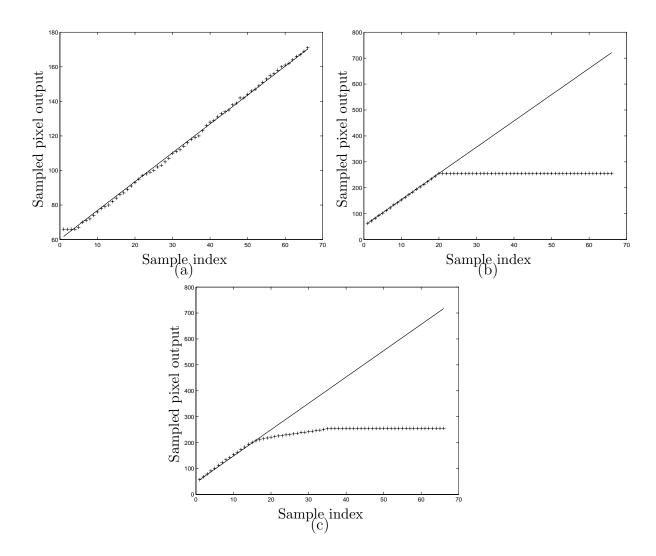

| 4.13 | Readout values (marked by '+' and estimated values (solid lines) for                    |    |

|      | (a) pixel in the dark area, (b) pixel in bright area, and (c) pixel with                |    |

|      | varying illumination due to motion                                                      | 74 |

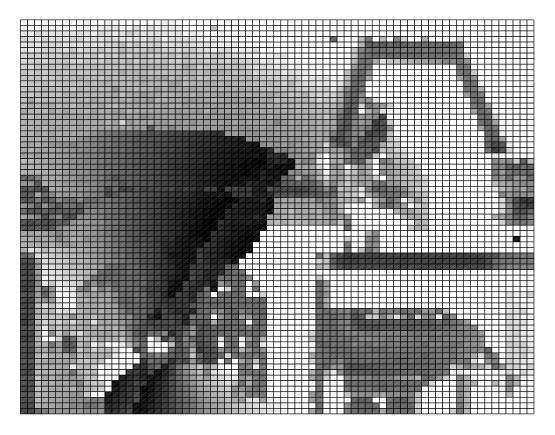

| 4.14 | The "adapted" exposure time for each pixel in the final image, where                    |    |

|      | the level of shade represents time (darker means shorter time)                          | 75 |

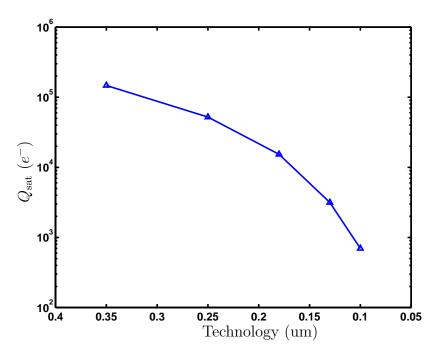

| 5.1  | Projected pixel well capacity as a function of technology scaling                       | 78 |

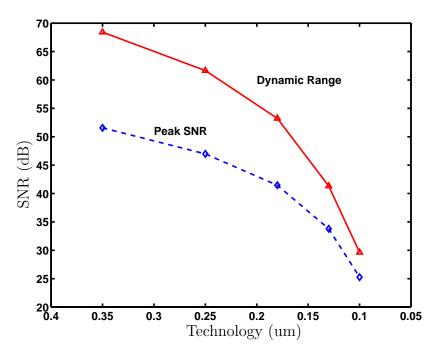

| 5.2  | Projected peak SNR and dynamic range as a function of technology                        |    |

|      | scaling                                                                                 | 79 |

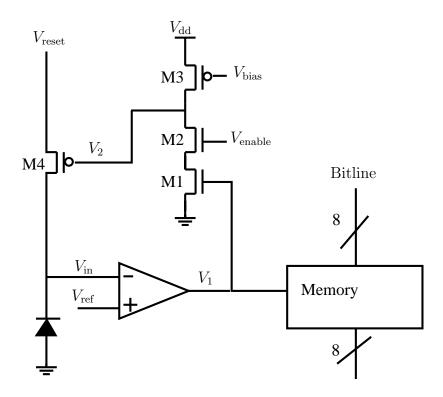

| 5.3  | Self-reset Digital Pixel Sensor circuit                                                 | 81 |

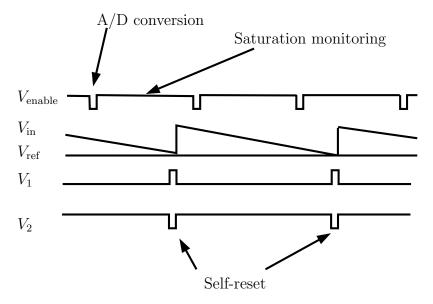

| 5.4  | Self-reset Digital Pixel Sensor timing diagram                                          | 81 |

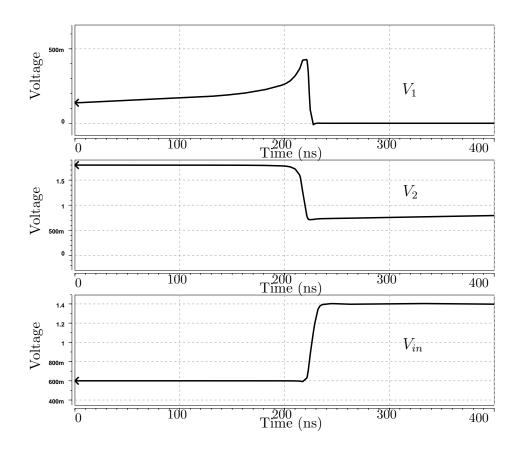

| 5.5  | HSPICE wave forms of $V_1$ , $V_2$ and $V_{\rm in}$ during self resetting for the pixel |    |

|      | circuit implemented in a standard $0.18\mu\mathrm{m}$ CMOS technology. The              |    |

|      | diode voltage $V_{\rm in}$ is reset from 0.6V to 1.4V in less than 90ns                 | 82 |

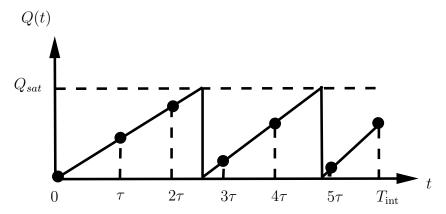

| 5.6  | Photocharge as a function of time for the self-reset pixel where self-                  |    |

|      | resetting happens twice during integration time $[0, T_{int}]$                          | 84 |

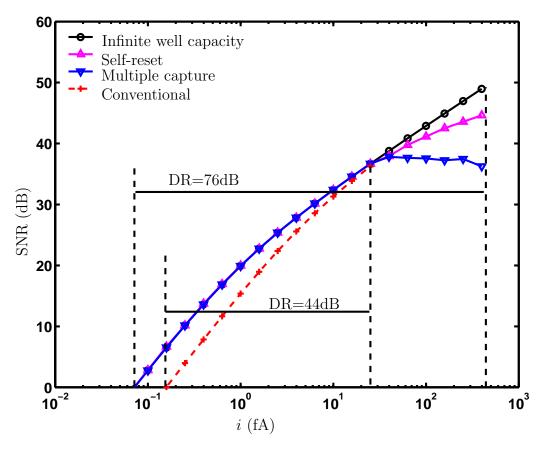

| 5.7  | SNR and dynamic range comparison with well capacity $Q_{\text{sat}} = 6250e^-$ ,        |    |

|      | readout noise of $30e^-$ , reset noise of $8e^-$ and total 32 multiple captures.        |    |

|      | The circled line is a sensor with infinite well capacity serving as a                   |    |

|      | theoretical upper bound                                                                 | 90 |

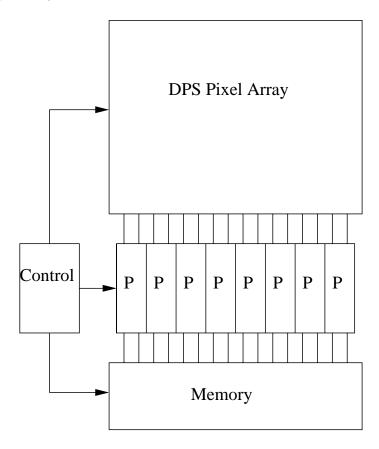

| 6.1  | Proposed a single chip imaging system architecture with column level                    |    |

|      | processors in [68]                                                                      | 95 |

|      |                                                                                         |    |

## Chapter 1

## Introduction

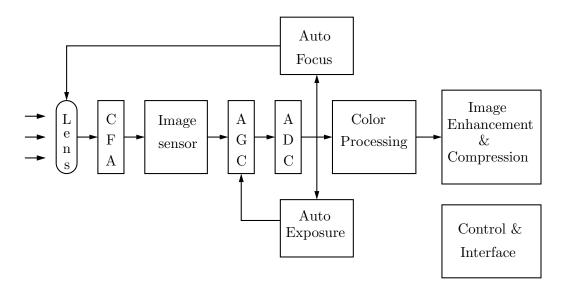

Digital cameras comprise a system of components that must work together and provide a high quality result. Figure 1.1 shows the block diagram of the components in a typical digital camera system. After passing through the lens and the color filter array (CFA), light is converted into electrical signal in the image sensor. The signal is amplified by the automatic gain control (AGC) and then converted into digital signal. Finally, the digital signal is processed and compressed before it stored as a digital image. The continued scaling of CMOS technology, together with the progress in the design of mixed-signal CMOS circuits, has enabled the integration of AGC, analog to digital converter (ADC), color processing and image compression functions into a single chip. To integrate the image sensor on the same chip with the rest circuits, however, a number of issues are yet to be solved.

The image sensor plays a pivotal role in the final image quality. Most of today's video and digital cameras use Charge-Coupled Devices (CCD). In these sensors, the electric charge collected by the photodetector array during exposure time is serially shifted out of the sensor chip, thus resulting in slow readout speed and high power consumption. CCD is fabricated using specialized process with optimized photodetectors, it has very low noise and good uniformity. Since this process is incompatible with the standard CMOS process, the CCD sensor can not be integrated on the same

Figure 1.1: A typical digital camera system.

CMOS chip with the rest circuitry.

Recently developed CMOS image sensors, by comparison, are read out non-destructively and in a manner similar to a digital memory and can thus be operated at very high frame rates. The CMOS image sensor can be integrated on the same chip, ultimately leading to a single-chip digital camera with very compact size, low power consumption and additional functionality. These appealing advantages of CMOS image sensors further expand their applications beyond traditional digital cameras, into fields such as PC cameras, mobile phones, PDAs, and automobiles. However, due to their high read noise and high fixed pattern noise (FPN), CMOS image sensors generally suffer from lower signal to noise ratio (SNR) and dynamic range than CCDs. Enhancing the SNR and dynamic range of CMOS image sensor, therefore, is a common goal that industry and research community are striving for.

This chapter first presents a review on the characteristics of solid state image sensors and the architectures of an interline CCD sensor and three CMOS image sensors — Passive Pixel Sensor (PPS), Active Pixel Sensor (APS), and Digital Pixel Sensor (DPS). The dominating factors in limiting sensor SNR and dynamic range are then discussed. Finally, previous work on image sensor dynamic range enhancement

is presented.

#### 1.1 Solid State Image Sensors

The image capturing devices in digital cameras are all solid state area image sensors. An area image sensor array consists of  $n \times m$  pixels, ranging from  $320 \times 240$  (QVGA) to  $7000 \times 9000$  (very high end astronomy sensor). Each pixel contains a photodetector and devices for readout. The pixel size ranges from  $15\mu\text{m} \times 15\mu\text{m}$  down to  $3\mu\text{m} \times 3\mu\text{m}$ , where the minimum pixel size is limited by dynamic range and cost of optics. Pixel fill factor is the fraction of pixel area occupied by the photodetector, which ranges from 0.2 to 0.9. High fill factor is always desirable.

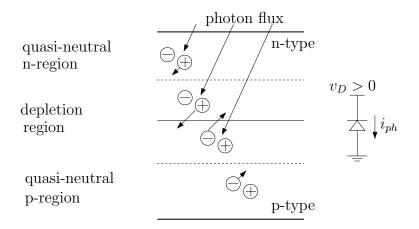

The photodetector [1] converts incident radiant power (photons/sec) into photocurrent that is proportional to the radiant power. There are several types of photodetectors, the most commonly used are the photodiode, which is a reverse biased pn junction, and the photogate, which is an MOS capacitor. Figure 1.2 shows the photocurrent generation in a reverse biased photodiode [3]. The photocurrent,  $i_{ph}$ , is the sum of three components: i) current due to generation in depletion (space charge) region,  $i_{ph}^{sc}$  — almost all carriers generated are swept away by strong electric field; ii) current due to holes generated in n-type quasi-neutral region,  $i_{ph}^{p}$  — some diffuse to space charge region and get collected; iii) current due to electrons generated in p-type region,  $i_{ph}^{n}$ . Therefore, the total photo-generated current is:

$$i_{ph} = i_{ph}^{sc} + i_{ph}^{p} + i_{ph}^{n}. (1.1)$$

The detector spectral response  $\eta(\lambda)$  is the fraction of photon flux that contributes to photocurrent as a function of the light wavelength  $\lambda$ , and the quantum efficiency (QE) is the maximum spectral response over  $\lambda$ .

The photodetector dark current  $i_{dc}$  is the detector leakage current, *i.e.*, current not induced by photogeneration. It is called dark current since it corresponds to the photocurrent under no illumination. Dark current is caused by the defects in silicon,

Figure 1.2: Photocurrent generation in a reverse biased photodiode

which include bulk defects, interface defects and surface defects. Dark current limits the photodetector dynamic range because it reduces the signal swing and introduces shot noise.

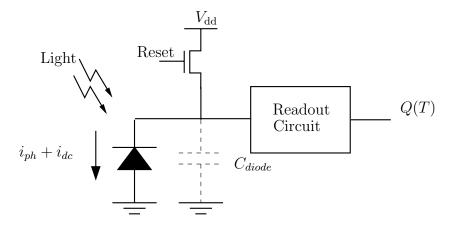

Since the photocurrent is very small, normally on the order of tens to hundreds of fA ( $10^{-15}$  Amp), it is integrated into charge and the accumulated charge (or converted voltage) is read out. This type of operation is called direct integration, the most commonly used mode of operation in an image sensor. In this operation, the photodiode is reset to the reverse bias voltage at the start of the image capture exposure time, or integration time. The diode current is integrated on the diode parasitic capacitance during integration time and the accumulated charge or voltage is read out at end.

#### 1.1.1 CCD Image Sensors

CCD image sensors [2] are the most widely used solid state image sensors in today's digital cameras. The primary difference between CCD and CMOS image sensors is the readout architecture. For CCDs, the integrated charge is shifted out using capacitors.

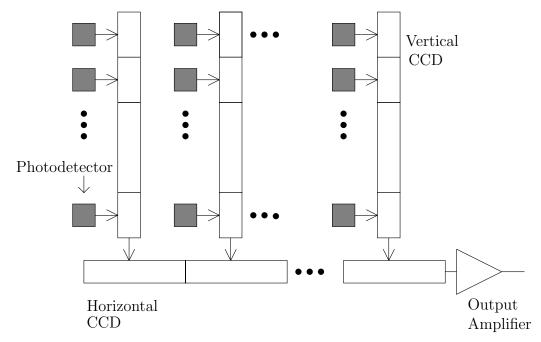

Figure 1.3 depicts the block diagram of the widely used interline transfer CCD image sensors. It consists of array of photodetectors and vertical and horizontal CCDs

for readout. During exposure, the charge is integrated in each photodetector, and it is simultaneously transferred to vertical CCDs at the end of exposure for all the pixels. The charge is then sequentially readout through the vertical and horizontal CCDs by charge transfer.

Figure 1.3: Block diagram of a typical interline transfer CCD image sensors.

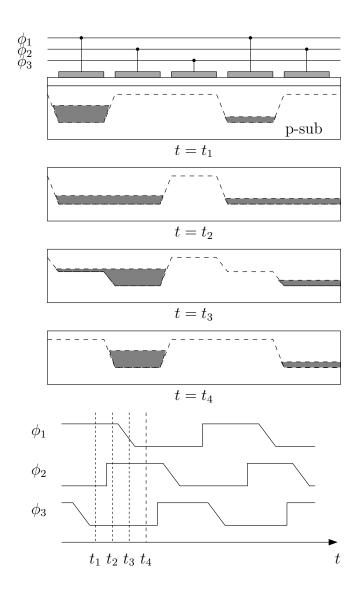

A CCD is a dynamic charge shift register implemented using closely spaced MOS capacitors clocked at different phases as shown in Figure 1.4. The capacitors operate in deep depletion regime when clock is high. Charge is transferred from one capacitor whose clock is switching from high to low, to the next capacitor whose clock is switching from low to high at the same time. During this transfer process, most of the charge is transferred very quickly by repulsive force among electrons, which creates self-induced lateral drift, the remaining charge is transferred slowly by thermal diffusion and fringing field.

The charge transfer efficiency describes the fraction of signal charge transferred from one CCD stage to the next. It must be made very high ( $\approx 1$ ) since in a CCD image sensor charge is transferred up to n+m CCD stages for a  $m\times n$  pixel sensor. The

Figure 1.4: Potential wells and timing diagram during the transfer of charge in a three-phase  ${\rm CCD}$

charge transfer must occur at high enough rate to avoid corruption by leakage, but slow enough to ensure high charge transfer efficiency. Therefore, CCD image sensor readout speed is limited mainly by the array size and the charge transfer efficiency requirement. As an example, the maximum video frame rate for an  $1024 \times 1024$  interline transfer CCD image sensor is less than 25 frames/s given a 0.99997 transfer efficiency requirement and  $4\mu m$  center to center capacitor spacing.

The biggest advantage of CCD is its high quality. It is fabricated using specialized process [2] with optimized photodetectors, very low noise, and very good uniformity. The photodetectors have high QE and low dark current. No noise is introduced during charge transfer. The disadvantages of CCD include: i) it can not be integrated with other analog or digital circuits such as clock generation, control and A/D conversion; ii) it is highly non-programmable; iii) it has very high power consumption because the entire array is switching at high speed all the time; iv) it has limited frame rate, especially for large sensors due to required increase in transfer speed while maintaining acceptable transfer efficiency.

Note that CCD readout is destructive, the pixel charge signal can only be readout once. The act of reading discharges the capacitor, eliminates the data.

#### 1.1.2 CMOS Image Sensors

CMOS image sensors [18]-[22] are fabricated using standard CMOS process with no or minor modification. The pixels in the array are addressed through the horizontal word line and the charge or voltage signal is readout from each pixel through the vertical bit line. The readout is done by transferring one row at a time to the column storage capacitors, then reading out the row using the column decoder and multiplexer. This readout method is similar to a memory structure. Figure 1.5 shows a CMOS image sensor architecture. There are three pixel architectures: Passive pixel (PPS), Active pixel (APS) and Digital pixel (DPS).

Figure 1.5: Block diagram of a CMOS image sensors.

#### Passive and Active Pixel Sensors

PPS [23]-[29] has only one transistor per pixel, as shown in Figure 1.6. The charge signal in each pixel is read out via a column charge amplifier, and this readout is destructive as in the case of CCD. PPS has small pixel size and large fill factor, but it suffers from slow readout speed and low SNR. PPS readout time is limited by the time of transferring a row to the output of the charge amplifiers.

APS [30]-[45] normally has three or four transistors per pixel where one transistor works as buffer and amplifier. As shown in Figure 1.7, the output of the photodiode is buffered using pixel level follower amplifier, therefore, output signal is in voltage and the reading is not destructive. In comparison to PPS, APS has larger pixel size and lower fill factor, but its readout is faster and has higher SNR.

Figure 1.8 shows a CMOS photogate APS pixel. The photogate PG is biased in deep depletion during integration and the photon induced charge is accumulated underneath the gate. Then during reading, the photogate voltage is lowered to 0V and the charge is transferred to the floating node D, which is reset to a certain

Figure 1.6: Passive pixel sensor (PPS)

Figure 1.7: Active Pixel Sensor (APS)

voltage prior to the charge transfer. The transfer gate TX can be either switched from low to high or kept at a constant intermediate voltage during the charge transfer. The output signal from the pixel is still in voltage that is converted by the floating node capacitance. The column and chip circuits of photogate APS are identical to photodiode APS.

Figure 1.8: Photogate APS

#### CMOS Digital Pixel Sensors

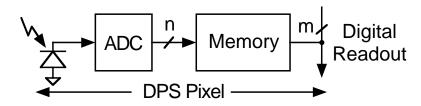

In a Digital Pixel Sensor (DPS) [52]-[60], each pixel has an ADC, all ADCs operate in parallel, and digital data stored in the memory is directly read out of the image sensor array as in a conventional digital memory (see Figure 1.9). The DPS architecture offers several advantages over analog image sensors, such as Active Pixel Sensors (APS). These include better scaling with CMOS technology due to reduced analog circuit performance demands and the elimination of read related column fixed-pattern noise (FPN) and column readout noise. With an ADC and memory per pixel, massively parallel "snap-shot" imaging, A/D conversion and high speed digital readout become practical, eliminating analog A/D conversion and readout bottlenecks. This

benefits traditional high speed imaging applications (e.g., [100, 101]) and enables efficient implementations of several still and standard video rate applications such as sensor dynamic range enhancement and motion estimation [65, 67, 66, 68].

Figure 1.9: Digital Pixel Sensor (DPS)

The main drawback of DPS is its large pixel size due to the increased number of transistors per pixel. Since there is a lower bound on practical pixel sizes imposed by the wavelength of light, imaging optics, and dynamic range considerations, this problem diminishes as CMOS technology scales down to  $0.18\mu m$  and below. Designing image sensors in such advanced technologies, however, is challenging due to supply voltage scaling and the increase in leakage currents [19].

Note that only DPS is capable of performing high-speed, non-destructive, "snap-shot" image capture. CCD and PPS readout is destructive; APS can not perform real "snap-shot" capture due to the different integration time for each row during exposure.

#### 1.2 SNR and Dynamic Range Enhancement

SNR and dynamic range are important figures of merit for image sensors. Dynamic range quantifies the sensor's ability to adequately image both high lights and dark shadows in a scene. CMOS image sensors generally suffer from high read noise and non-uniformity, resulting in lower SNR and dynamic range than CCDs. In this section, after quantifying sensor SNR and dynamic range and discussing their dependencies on key sensor parameters, we will review previous works on image sensor dynamic range enhancement.

#### 1.2.1 SNR and Dynamic Range

Figure 1.10: CMOS image sensor pixel model.

Figure 1.10 shows a typical CMOS image sensor pixel operating in direct integration. The photodiode is reset before the beginning of capture. During exposure, the photocurrent is integrated onto the photodiode parasitic capacitor  $C_{diode}$  and the charge Q(T) (or voltage) is read out at the end of exposure time T. Dark current  $i_{dc}$  and additive noise are also integrated with the photocharge. The noise can be expressed as the sum of three independent components:

• Shot noise U(T), which is generated when current passes through the diode

junction, can be approximated by a Gaussian  $U(T) \sim \mathcal{N}(0, q \int_0^T (i_{ph}(t) + i_{dc}) dt)$  when photocurrent is large enough. Here q is the electron charge.

- Reset noise (including offset fixed pattern noise (FPN)), which is generated during reset, also has a Gaussian distribution,  $C \sim \mathcal{N}(0, \sigma_C^2)$ .

- Readout circuit noise V(T) (including quantization noise) with zero mean and variance  $\sigma_V^2$ .

Therefore the output charge from a pixel can be expressed as

$$Q(T) = \int_0^T (i_{ph}(t) + i_{dc})dt + U(T) + V(T) + C,$$

(1.2)

provided  $Q(T) \leq Q_{sat}$ , the saturation charge, also referred to as well capacity.

If photocurrent is constant over exposure time, signal-to-noise ratio (SNR) is given by

$$SNR(i_{ph}) = 20 \log_{10} \frac{i_{ph}T}{\sqrt{q(i_{ph} + i_{dc})T + \sigma_V^2 + \sigma_C^2}}.$$

(1.3)

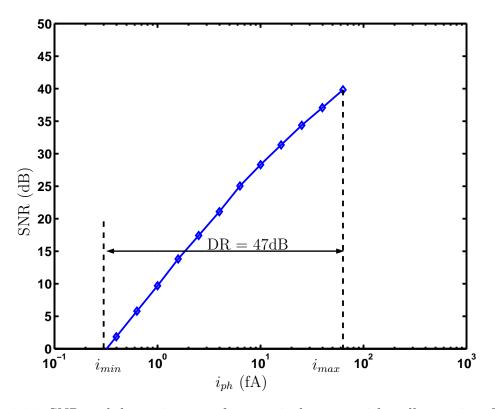

Equation 1.3 shows that SNR increases with  $i_{ph}$ , first at 20dB per decade when reset and readout noise variance dominates, and then at 10dB per decade when shot noise variance dominates. Since SNR also increases with T, it is always preferred to have the longest possible exposure time. Saturation and change in photocurrent due to motion, however, set an upper limit on exposure time.

Sensor dynamic range quantifies the ability to adequately image both high lights and dark shadows in a scene. It is defined as the ratio of the largest non-saturating photocurrent  $i_{max}$  to the smallest detectable photocurrent  $i_{min}$ , typically defined as the standard deviation of the noise under dark conditions. For a sensor with fixed well capacity  $Q_{sat}$ , saturation limits the highest signal and sensor read noise limits the lowest detectable signal. Using the sensor model, the dynamic range can be expressed as

$$DR = 20 \log_{10} \frac{i_{max}}{i_{min}} = 20 \log_{10} \frac{Q_{sat}}{\sqrt{qi_{dc}T + \sigma_V^2 + \sigma_C^2}}.$$

(1.4)

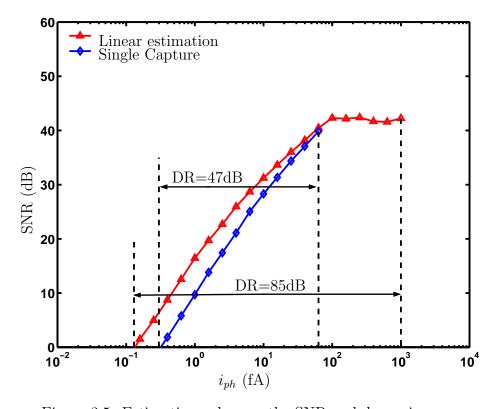

Figure 1.11: SNR and dynamic range for a typical sensor with well capacity,  $Q_{well}=18,750e^-$ , readout noise,  $\sigma_V=60e^-$ , reset nois,  $\sigma_C=62e^-$ , and total integration time,  $T=32\mathrm{ms}$ .

Figure 1.11 plots the SNR and dynamic range vs. photocurrent for a typical sensor. In this specific example, given a well capacity,  $Q_{well} = 18,750e^-$ , readout noise,  $\sigma_V = 60e^-$ , reset nois,  $\sigma_C = 62e^-$ , and total integration time, T = 32ms, the sensor dynamic range is 47dB and the peak SNR is less than 40dB. This dynamic range is not high enough to capture a typical outdoor scene where both bright sun light and dark shadow exist.

#### 1.2.2 Review of Dynamic Range Enhancement Schemes

Several techniques and architectures [71]-[95] have been proposed for extending image sensor dynamic range. Below is a review of some representative schemes.

#### Well capacity adjusting

In [81, 82], a well capacity adjusting scheme was proposed to enhance the sensor dynamic range. In this scheme, the well capacity is increased one or more times during integration. For APS, this is done by adjusting the reset signal one or more times during integration [83]. As a result, pixel current to charge transfer function is compressed, and the maximum non-saturating current is extended.

The increase in dynamic range, however, comes at the expense of decrease in SNR, as shown in [65]. Moreover, the smallest detectable signal does not change in this scheme, so dynamic range is only enhanced at high illumination end.

#### Multiple capture

In [80, 102], a multiple capture scheme was proposed to enhance the sensor dynamic range. The idea is to capture several images at different times within the normal exposure time — shorter exposure time images capture the brighter areas of the scene while longer exposure time images capture the darker areas of the scene. A high dynamic range image is then synthesized from the multiple captures by appropriately scaling each pixel's last sample before saturation.

In [65], it was shown that this scheme achieves higher SNR than well capacity adjusting scheme. However, this scheme does not take full advantage of the captured images. Since readout noise is not reduced, dynamic range is only extended at the high illumination end.

#### Spatially varying exposure

Another dynamic range enhancement scheme is spatially varying exposure [84, 85], which implements multiple capture using a conventional sensor by sacrificing spatial resolution. The idea is to deposit an array of neutral density filters on the sensor so that in a single capture pixels with darker filters sample high lights while pixels with lighter filters sample low lights. The high dynamic range image is synthesized using low pass filtering or more sophisticated techniques such as cubic interpolation.

This scheme is very simple to implement and requires no change to the sensor itself; however, the blocking of light due to neutral density filters reduces sensor sensitivity and SNR. Also, very high resolution sensor is needed since the spatial resolution is reduced. The dynamic range is extended at the high illumination end only, which is same as the above two schemes.

#### Time-to-saturation

In [86, 87, 88], a time to saturation scheme was proposed. The idea is to measure the integration time required to saturate each pixel. In this scheme, the minimum detectable current is limited by the maximum allowable integration time and the maximum detectable current is limited by circuit mismatches, readout speed and FPN.

The challenge in implementing this scheme is to find a way to detect saturation for each pixel, and then record the time — if global circuits are used, contention can severely limit performance; if the detection and recording are done at the pixel level, the pixel size may become unacceptably large. The sensor SNR is quite uniform at all signal levels, and the peak SNR is limited by the well capacity.

#### Logarithmic sensor

In a logarithmic sensor [89, 90, 91], the photocurrent is directly converted to voltage for readout. The sensor achieves high dynamic range via logarithmic compression during conversion to voltage via the exponential I-V characteristics of the MOS transistor in subthreshold. Up to 5-6 decades of dynamic range can be compressed into a voltage range around 0.5V depending on the transistor threshold voltage and the number of series transistors.

There are several issues associated with this scheme. First of all, transistor mismatches are significant due to the poorly defined subthreshold MOSFET characteristics as well as varying threshold voltages. Second, succeeding circuitry must be extremely precise to make use of the dynamic range afforded by the compressed output voltage. Finally, the non-integrating nature limits the achievable SNR in even high illumination due to the exponential transconductance relationship.

#### 1.3 Organization

Previously proposed high dynamic range enhancement schemes mainly focus on extending the sensor dynamic range at high illumination end, sensor dynamic range extension at low illumination has not been addressed. For some schemes, the increase in dynamic range comes at the expense of decrease in SNR; and for others, SNR is the same since sensor readout noise is not reduced. Moreover, all the previous schemes are subject to potential motion blur, which limits the maximum exposure time and hence SNR at both low and high illumination ends.

In this dissertation, a new pixel architecture and algorithm are presented that enhance SNR and dynamic range of CMOS image sensors at both low and high illumination ends, and simultaneously eliminate motion blur. Our algorithm takes advantage of the unique high speed, multiple non-destructive operation of CMOS Digital Pixel Sensor, as we will demonstrate using a 10,000 frames/s DPS chip in Chapter 2. The algorithm consists of two main procedures – photocurrent estimation and motion/saturation detection. Estimation is used to reduce read noise and thus to

enhance dynamic range at the low illumination end. Besides the saturation detection used to enhance dynamic range at the high illumination end, a motion blur detection algorithm is added to ensure that the estimation is not corrupted by motion. This motion blur detection further makes it possible to extend exposure time and to capture more images, which can be used to further enhance dynamic range at the low illumination end.

Finally, to solve the problem with CMOS technology scaling and further enhance sensor SNR at high illumination, a self-resetting architecture is presented. In this architecture, each pixel resets itself one or more times during exposure time as a function of the illumination level, resulting in higher effective well capacity and thus higher SNR. Further SNR and dynamic range improvement is achieved by utilizing our photocurrent estimation and saturation/motion detection algorithm by taking new noise components into consideration. As will be shown, simulation results demonstrate significant dynamic range and SNR improvements.

This dissertation is organized into six chapters of which this is the first. Chapter 2 presents a 352 × 288 pixel DPS test chip that demonstrates the high speed, non-destructive readout advantages of CMOS digital pixel image sensor. Chapter 3 presents three photocurrent estimation algorithms that can be used to reduce read noise and enhance dynamic range at the low illumination end. Chapter 4 presents a new method that synthesizes the high dynamic range, motion blur free image from multiple image captures, motion/saturation detection algorithms. Experimental results achieved with this algorithm are also presented. In Chapter 5, a self-reset architecture to solve the reduced well capacity problem associated with CMOS technology scaling is presented. By extending our photocurrent estimation and motion/saturation detection algorithm into this new architecture, the SNR and dynamic range of CMOS image sensor are further improved. Finally, in Chapter 6, the contributions of this research are summarized, and directions for future work are suggested.

# Chapter 2

# A 10,000 Frames/s Digital Pixel

### Sensor

Several high speed CMOS APS chips have been reported. Krymski et.~al.~[104] describe a  $1024 \times 1024$  APS, followed by column-level 8-bit ADCs that achieves over 500 frames/s. Readout and digitization are performed one row at a time and each digitized row is read out over a 64-bit wide output bus. Fully pixel-parallel image acquisition ("snap shot" acquisition) and short shutter durations are important requirements in high speed imaging to prevent image distortion due to motion. These requirements, however, cannot be achieved using the standard APS architecture used in [104]. To address this limitation, Stevanovic et.~al.~[105] describe a  $256 \times 256$  APS with per-pixel storage capacitor to facilitate pixel-parallel image acquisition. Analog pixel values are multiplexed and read out through 4 analog outputs, achieving over 1000 frames/s.

Moving ADC from column/chip level into pixel level not only reduces the stringent requirement of signal integrity when shifting the analog signal out from the pixel array, it also reduces the time requirement in digitizing the signals from all the pixels [52].

This is a key advantage of DPS over APS employing column-level, chip-level, or off-chip ADCs where digitization rates do not scale linearly with the number of pixels in the array. Storing the instantaneous data into the digital memory embedded in each pixel further increase the frame rate for a given I/O bandwidth since the sensor integration and readout phases can now be overlapped.

The DPS architecture (see Figure 2.1) described in this chapter fulfills the requirements of high speed imaging with practically no limit on array size. It performs fully pixel-parallel image acquisition. Pixel reset is performed in parallel for all pixels and the reset duration is completely programmable, permitting higher shutter speeds. The massively-parallel per-pixel A/D conversion scheme demonstrated here results in a high digitization rate.

Figure 2.1: Simple DPS pixel block diagram.

In this chapter, the DPS chip architecture and main characteristics are first presented. Next, the circuit implementation of the pixel design is presented and the chip operation including the different imaging modes is discussed. Finally, in Section 2.4, experimental measurements of the chip characteristics including ADC performance, QE, dark current, noise, digital noise coupling, and sample images are presented.

#### 2.1 DPS Chip Overview

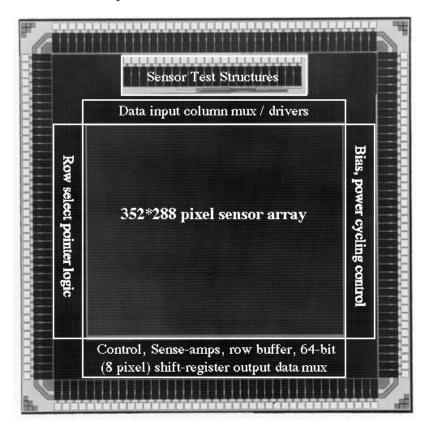

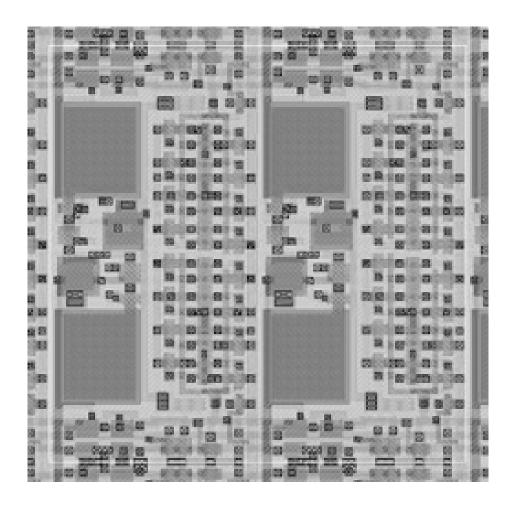

A photomicrograph of the DPS chip is shown in Figure 2.2 and the main chip characteristics are listed in Table 2.1. The chip contains 3.8 million transistors on a  $5 \times 5$ mm die. The sensor array is  $352 \times 288$  pixels in size, conforming to the CIF format. The

pixel is  $9.4\mu$ m on each side and contains 37 transistors, including a photogate, transfer gate, reset transistor, a storage capacitor, and an 8-bit single-slope ADC with an 8-bit 3T-DRAM. The chip also contains test structures that we used for detailed characterization of APS and DPS pixels [107]. The test structures can be seen in upper center area of the chip.

Figure 2.2: DPS Chip photomicrograph. The chip size is  $5 \times 5$ mm.

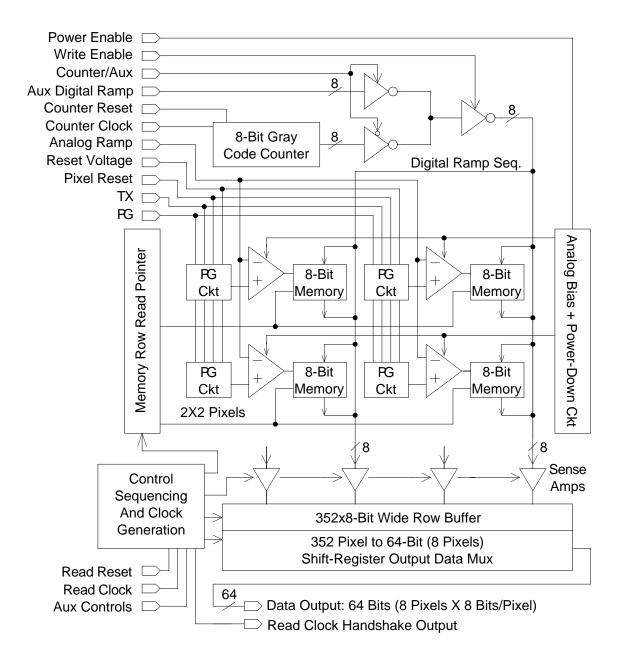

Figure 2.3 shows a block diagram of the DPS chip. At the center is the sensor array. The periphery above the sensor core contains an 8-bit gray code counter, an auxiliary code input, and multiplexers and tri-state column data drivers that are used to write data into the memory within the pixel array. The column multiplexers can be used to substitute arbitrary patterns for the standard gray code during data conversion. This facilitates the use of nonlinear ADC transfer functions, for example, for compression of dynamic range and contrast stretching. To the left of the sensor

| Technology                  | $0.18\mu \text{m}$ 5-metal CMOS |

|-----------------------------|---------------------------------|

| Die size                    | $5 \times 5 \text{ mm}$         |

| Array size                  | $352 \times 288$ pixels         |

| Number of transistors       | 3.8 million                     |

| Readout architecture        | 64-bit (167 MHz)                |

| Max output data rate        | $> 1.33 \; GB/s$                |

| Max continuous frame rate   | > 10,000  frames/s              |

| Max continuous pixel rate   | > 1 Gpixels/s                   |

| Pixel size                  | $9.4 \times 9.4 \mu \mathrm{m}$ |

| Photodetector type          | nMOS Photogate                  |

| Number of transistors/pixel | 37                              |

| Sensor fill factor          | 15%                             |

Table 2.1: Chip characteristics.

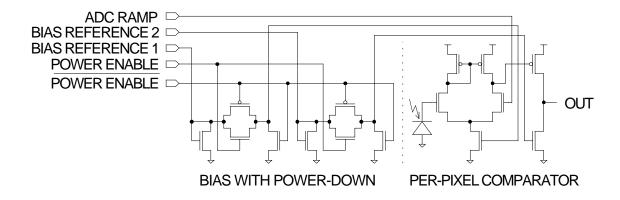

array is the readout control periphery that includes a row select pointer for addressing the pixel-level memory during readout. To the right of the sensor array is the bias generation and power-down circuits, which are used to digitally control the per-pixel ADC and memory sense-amp biases. The analog ramp signal input to the array needed for the per-pixel ADCs is supplied by an off-chip DAC.

Below the sensor core is the digital readout circuits that include column sense-amps for reading the pixel-level memory and an output multiplexing shift register. The pixel values are read out of the memory one row at a time using the row select pointer and column sense-amps. Each row is then buffered and pipelined so that as one row is being shifted out of the chip the following row is read out of the memory. A 64-bit wide parallel-in, serial-out shift-register bank was used instead of a large multiplexer since in a shift register data moves in small increments, reducing local capacitance and drive circuit performance requirements. With each clock cycle, eight 8-bit pixel values are read out in a continuous stream with no waits or gaps between rows. An entirely closed-loop clocking system is used to assure clock and data integrity. The 64-bit output bus is clocked at 167 MHz for a 1.33 GB/s readout rate.

In the lower left corner of the chip is the readout control block. Since the chip is to be clocked at upwards of 167 MHz, it was important to keep off-chip high speed

Figure 2.3: DPS block diagram.

controls to a minimum. The control block provides all the signals needed for readout from a single frame reset followed by a single continuous clock burst. A 6-phase clock generator using feedback to ensure correct margins is used to drive the shift registers. During chip testing or experimental operation, the control block can be bypassed and a set of auxiliary input controls used. Almost all digital circuitry in the periphery of the chip was designed using static logic to permit arbitrarily low clock rates.

# 2.2 Pixel Design

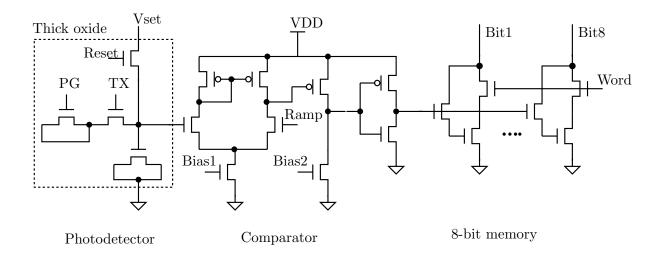

The pixel circuit is shown in Figure 2.4. It consists of a photogate circuit, a comparator and an 8-bit memory. The photogate circuit consists of an nMOS photogate, a transfer gate, a reset transistor and a sample capacitor. We decided to use a photogate to achieve high conversion gain and because preliminary process data indicated that native photodiodes have unacceptably high leakage. We implemented the photogate circuit using the standard thick oxide (3.3V) transistors that normally used in I/O circuits, to avoid the high gate and subthreshold leakage currents of the thin oxide (1.8V) transistors. Implementing the photogate and reset transistor using thick oxide transistors also makes it possible to use higher gate voltages than the nominal 1.8V supply to increase voltage swing.

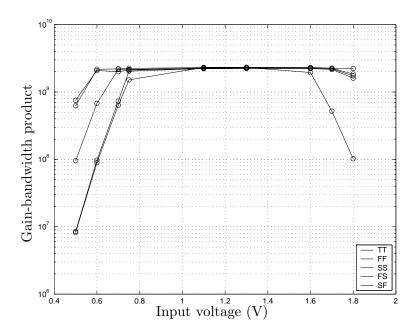

The comparator consists of a differential gain stage, a single-ended gain stage, followed by a CMOS inverter. It is designed to provide gain sufficient for 10-bits of resolution with an input swing of 1V and a worst case settling time of 80ns. This provides the flexibility to perform 8-bit A/D conversion over a 0.25V range in under  $25\mu$ s, which is desirable for high speed and/or low light operation. In our earlier implementation [58], the pixel-level comparator was configured as a unity feedback amplifier during reset to perform auto zeroing. Since in this implementation we needed very high gain-bandwidth product at low power consumption and small area, we chose to run the comparator open loop and sacrifice the auto zeroing capability. To cancel the high comparator offset voltages we rely on digital CDS. Due to the low operating

Figure 2.4: Pixel schematic.

voltage and the desire for a large input swing, we could not use a cascode architecture. Instead we used a three stage architecture, with a CMOS inverter as the third stage to saturate the output voltage levels. Figure 2.5 plots the simulated comparator gain-bandwidth product vs. input voltage at all fabrication corners (normal, fast-fast, fast-slow, slow-fast, slow-slow).

The pixel-level memory was implemented using 3T dynamic memory cells with a single read/write port to achieve small area and high speed readout. The memory was designed for a maximum data hold time of 10ms. This required the use of larger than minimum gate length access transistors and holding the bit lines at around Vdd/2 to combat high transistor off-currents. Writing into the memory is locally controlled by the comparator. During readout, single-ended charge-redistribution column sense-amps, located in the periphery and not shown in the figure, are used for robustness against the effects of capacitive coupling between the closely spaced bit lines.

The comparator and pixel-level memory circuits can be electrically tested by applying analog signals to the sense node through the  $V_{\rm set}$  signal, performing A/D conversion using the normal input ramp and the on-chip gray-code generator, and then reading out the digitized values. In this way, except for the photodetectors, the DPS chip can be electrically tested and characterized without the need for light or optics.

Figure 2.5: Comparator gain-bandwidth product vs. input voltage.

Figure 2.6 shows the layout of a 2×2 pixel block. The four large squares are the photogates, which are sized and spaced equally in the horizontal and vertical dimensions. The fill factor of this pixel is 15%. The silicide layer, which is opaque, was blocked from the photogates. The 3-stage comparators are seen near the top and bottom of the pixel quad. The digital memory is located in the two sections near the center of the quad. The smaller squares are the capacitors, with the transfer and reset transistors near by.

The pixels are mirrored about the horizontal axis in order to share the n-well and some of the power and bias lines. With digital CDS as discussed in Section 2.3, we did not observe any offset FPN due to mirroring. A small layout asymmetry, however, has resulted in odd/even row gain FPN. Memory bitlines (metal 3) and digital ground (metal 1) run vertically over the memory, while analog signal (metal 2) and power distribution (metal 4) run horizontally on top of the comparators. Metal 5 covers most of the array and acts as a light shield. Pixel array analog and digital grounds are kept separate in order to reduce noise coupling from the digital memory into the sensitive analog components.

Figure 2.6: DPS pixel layout (2  $\times$  2 pixel block shown). Pixel size is  $9.4 \times 9.4 \mu m$ .

# 2.3 Sensor operation

In this section we describe the details of the DPS chip operation. First we describe the A/D conversion operation. Next we discuss the basic imaging modes of operation including single frame capture, digital correlated double sampling, high speed operation, and multiple image capture.

## 2.3.1 A/D conversion operation

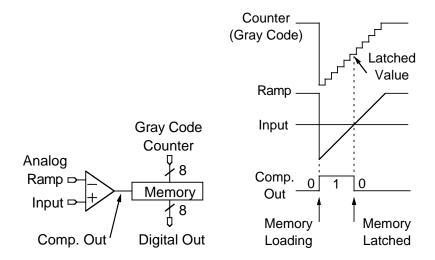

Figure 2.7 illustrates the per-pixel single-slope A/D conversion technique used in our chip. The globally distributed voltage ramp is connected to each pixel's comparator inverting ("-") input. The non-inverting ("+") input on each comparator is directly connected to the sense node. The globally distributed gray coded counter values, shown as a stepped "digital ramp," are simultaneously applied to the per-pixel memory bit lines.

Figure 2.7: Single-slope ADC operation.

At the beginning of conversion, the ramp voltage is lowered to just below the lowest expected sense node voltage, which sets the comparator output to high. This enables the per-pixel memory to begin loading the gray code values. The ramp is

then swept linearly until it exceeds the reset voltage. Simultaneously, the gray code counter sweeps across an equivalent set of values (256 for 8 bits). As the ramp crosses each pixel's sense node voltage, its comparator output switches low, and the gray code value present at that moment is latched in the pixel's memory. At the end of conversion, each pixel's memory contains an 8-bit gray coded value that is a digital representation of its input voltage.

Although using a linear ramp is the typical approach, it is possible to use alternative ramp profiles such as piecewise linear or exponential curves that compress or expand different illumination ranges. It is also possible to change the gain of the A/D conversion by changing the voltage range of the analog ramp. One may also use alternate sequences for the digital inputs using the auxiliary inputs.

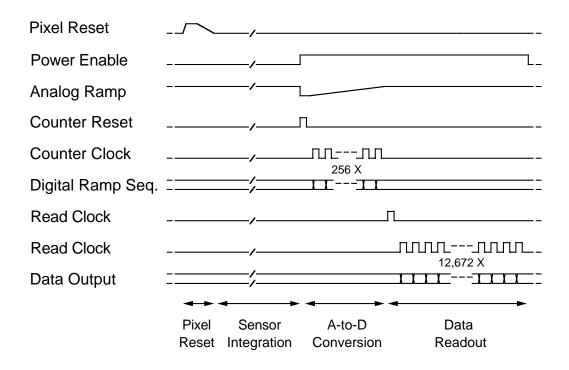

#### 2.3.2 Imaging modes

Figure 2.8 depicts a simplified timing diagram for the DPS chip. Operation can be divided into four main phases: reset, integration, A/D conversion, and readout. The reset, integration and A/D conversion phases occur completely in parallel over the entire array, *i.e.*, in "snap-shot" mode, thus avoiding image distortion due to the row by row reset and readout of APS. To minimize charge injection into the sense node, which causes high FPN, a shallow reset signal falling edge is used. Sensor integration is limited by dark current or signal saturation on the long end and by internal time constants on the short end. Practical lower and upper bounds on integration time were found to be under  $10\mu$ s to well over 100ms.

After integration, per-pixel single-slope A/D conversion is simultaneously performed for all pixels, as discussed in the previous subsection. Typical conversion time is  $25\mu$ s, and can be as low as  $20\mu$ s at the highest frame rates. After conversion, readout commences. The readout of one frame is completed in around  $75\mu$ s.

Figure 2.9 shows the bias generation circuits for the pixel-level comparators, including the power-down circuitry. It consists of two sections, each with a current mirror, a transmission gate and a pull-down transistor. The comparators and the sense amps are turned on only during A/D conversion and readout phases by raising

Figure 2.8: Simplified DPS timing diagram.

Figure 2.9: Comparator bias generation with power-down.

the Power Enable control. Power cycling is not essential, but since full frame conversion and readout can be accomplished in as little as  $100\mu$ s, it can save several orders of magnitude of power when the chip is running at low frame rates and hence low A/D conversion/readout duty cycles.

The current mirrors divide down the external references ("Bias1, Bias2") by a factor of 100 in order to reduce the impedance of the external references for higher noise immunity. The transmission gates, operated by "Power Enable" and its complement, control whether the current mirror outputs are connected to the pixel array. When they are not connected, a pull-down transistor in each bias section connects the bias lines to ground, which shuts off the current source transistors in the two biased comparator stages. The circuits were designed, based on the loading of the  $352 \times 288$  pixel array, to power down or up within 100ns.

#### (A) Single sample:

## (B) Correlated double sample:

# (C) Multiple sampling:

(D) Continuous high speed operation with overlapping read:

Figure 2.10: Basic DPS operation schemes.

The DPS chip operation is quite flexible. The timing and order of different phases can be easily programmed for different imaging applications. Figure 2.10 illustrates some of the possible imaging modes of the chip. Mode (A) is the single frame capture scenario we detailed in the previous subsection. At low speeds, each phase can be kept completely separate so that, for example, noise coupling due to digital readout need not influence the sensor reset, integration or conversion. Mode (B) is used to implement digital correlated double sampling by converting and reading a "reset frame" right after reset. The digitized reset frame is subtracted from the digitized image frame externally. This is a "true" CDS operation, albeit digital in nature, in the sense that the two frames are taken after the same reset. Since a full frame conversion and readout can be completed in  $100\mu$ s or less, more frames can be converted and read out during a single exposure time. This is denoted by mode (C) in Figure 2.10. For example, in a typical 30ms exposure time, tens or even hundreds of frames can be converted and read out. This "oversampling" can be used to implement several image enhancement and analysis applications such as dynamic range enhancement, motion estimation and compensation, and image stabilization. At the highest speeds, one can overlap and pipeline phases to maximize integration time and thus reduce the amount of illumination needed, as illustrated in mode (D). For example, at 10,000 frames/s, the combined reset, A/D conversion and readout time closely approaches the full frame period. By overlapping integration with readout of the previous frame, integration time can be increased from close to zero to about  $75\mu$ s out of the  $100\mu$ s frame period.

# 2.4 Testing and characterization

The DPS chip has been tested and characterized and shown to be fully functional. In the following subsections, we present the electrical, optical, and noise characterization results, and show results demonstrating that digital readout noise has little or no effect on the imaging performance of the chip.

#### 2.4.1 Electrical and optical characterization results

Table 2.2 summarizes the DPS characterization results. Of particular interest is the measured average power consumption of only 50mW at 10,000 frames/s. The pixel-level comparators consume around 30mW of static power, while the digital readout circuits consume around 20mW of dynamic power. The poor imaging performance of the standard 0.18 $\mu$ m CMOS process resulted in high dark signal of 130mV/s and low QE of 13.6%. With conversion gain of 13.1 $\mu$ V/e<sup>-</sup>, sensitivity was just over 0.1V/lux.s. Dark current and QE can be significantly improved with minor process modifications that should not significantly affect pixel area or chip performance. The ADC integral nonlinearity (INL) was measured over the maximum useful input range of 1V, at a typical 1,000 frames/s, without correlated double sampling, and averaged for all pixels. It was found to be 0.22% or 0.56 LSB. We also found that reducing the swing to 0.9V improves INL to 0.1% or 0.25 LSB.

| Power used at 10K fps        | 50 mW, typical                            |

|------------------------------|-------------------------------------------|

| ADC architecture             | Per-pixel single-slope                    |

| ADC resolution               | 8-bits                                    |

| ADC conversion time, typical | $\sim 25\mu s$ , ( $\sim 20\mu s$ , min.) |

| ADC range, typical           | 1 V                                       |

| ADC integral nonlinearity    | < 0.22% (0.56  LSB)                       |

| Dark current                 | $130 \text{ mV/s}, 10 \text{ nA/cm}^2$    |

| Quantum efficiency           | 13.6%                                     |

| Conversion gain              | $13.1 \; \mu V/e^{-}$                     |

| Sensitivity                  | 0.107  V/lux.s                            |

| FPN, dark w/CDS              | $0.027\% \ (0.069 \ LSB)$                 |

| Temporal noise, dark w/CDS   | $0.15\% \ (0.38 \ LSB)$                   |

Table 2.2: DPS chip characterization summary. All numbers, except for power consumption are at 1000 frames/s.

To determine dark current, conversion gain, and QE of the DPS pixel, our chip included single pixel APS and DPS test structures that can be individually accessed and whose sense node voltages can be directly readout. The test structures are described in detail in [107]. For completeness, we provide the results that are relevant to the DPS chip.

The measured quantum efficiency curve for the photogate is shown in Figure 2.11. The maximum QE is around 13.6% at wavelegth of 600nm. The major reason for the low QE is the high recombination rate in the highly doped substrate.

Figure 2.11: Measured quantum efficiency.

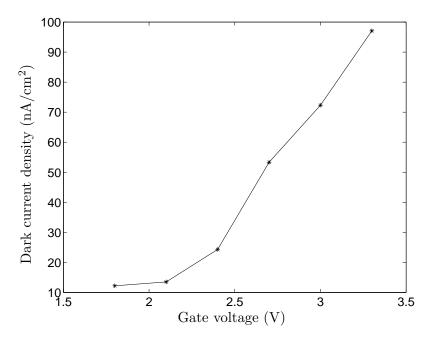

The measured dark current density was found to increase superlinearly with reverse bias voltage as shown in Figure 2.12. Since lowering PG voltage was also found to have little effect on QE [107], we typically operated PG at 2.1V or less.

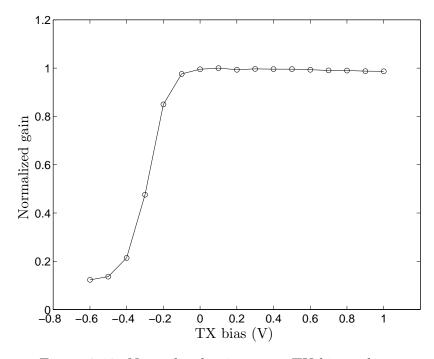

We found that the transfer transistor of the photogate circuit suffered from high off-current in spite of using a thick oxide transistor. We performed an experiment to find out the transfer gate voltage needed to turn it off. Figure 2.13 plots the normalized quantum efficiency of the photogate device for TX voltage from 1V down to -0.6V. During the experiment, the reset voltage is kept at 1.15V and PG is pulsed between 0 and 2.1V. It is clear that the transfer gate cannot be turned off unless the gate voltage (TX) is negative.

Since the transfer gate cannot be turned off using non-negative TX voltages, we often operated the photogate as a photodiode by setting both PG and TX voltages to

Figure 2.12: Measured photogate leakage current as a function of gate voltage.

Figure 2.13: Normalized gain versus TX bias voltage.

optimum fixed voltages. We found that QE in this mode is only slightly lower than when operating in the normal photogate mode. In this photodiode mode, however, ADC linearity is slightly compromised at high frame rates, since integration continues during A/D conversion.

#### 2.4.2 Temporal Noise and FPN

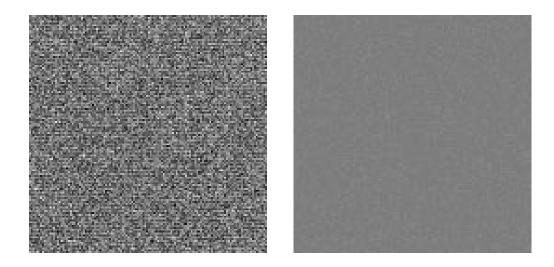

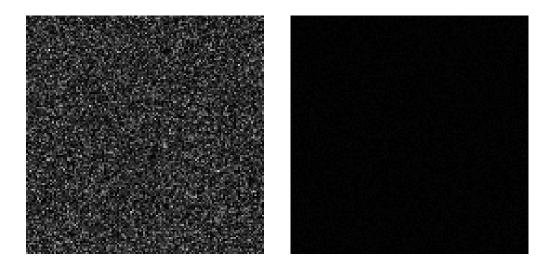

Figure 2.14: Images of fixed pattern noise without digital CDS (left) and with digital CDS (right) for an integration time of 1ms.

Correlated double sampling is perhaps the simplest example of how multiple image acquisitions within one integration can improve image quality. With digital CDS, FPN due to comparator offset and reset transistor threshold voltage and reset temporal noise are greatly reduced. In Figure 2.14, two images rendered using the same scale, show fixed pattern noise with and without correlated double sampling (performed digitally off-chip). On the left one can see significant noise that is primarily due to random variations in the pixel-level ADC comparator offset voltages. This random pattern of noise tends to be less visually objectionable than column fixed pattern noise, common in typical analog APS designs, that results in streaks. On

the right is the result after external digital CDS. The FPN has been reduced from 0.79% to 0.027%, RMS, a reduction by nearly a factor of 30. The final FPN number is about 1/15th of an LSB.

Figure 2.15: Images of temporal noise without digital CDS (left) and with digital CDS (right).

Figure 2.15 shows two images of temporal noise, with and without CDS, using a 1ms integration time, in the dark. In this case, the images show the variability in pixel values over time, with FPN removed. Using digital CDS, temporal noise has been reduced from 1.6% to 0.15% RMS, which is less than 1/3 of an LSB.

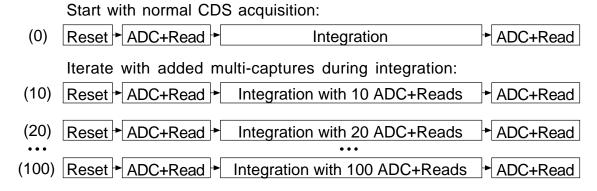

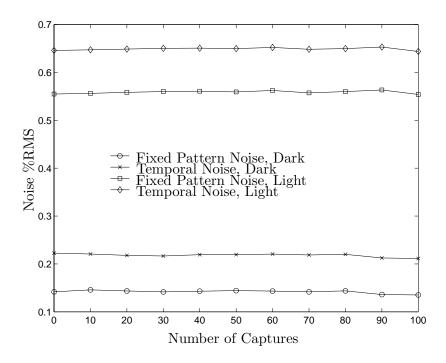

## 2.4.3 Digital noise coupling

Since DPS operation involves per-pixel digitization, digital pixel readout and highspeed I/O switching during integration, it is important to investigate the impact of digital coupling on the sensor performance. This is an especially important question given the ability of the DPS architecture to take hundreds of image samples within a single integration. To examine this issue, we devised the experiment explained with the aid of Figure 2.16. The experiment was conducted under worst-case noise conditions, where the total integration time was minimized and the time spent converting and reading out was maximized to the point of being continuous.

Figure 2.16: Digital read-induced noise experiment.

The experiment consisted of 11 sets of measurements. In the first set we performed a reset followed by an A/D conversion and a readout, integrated for 24ms, and then performed a final A/D conversion and a readout. Digital CDS was performed on the two captures to increase the sensitivity of the measurements. This is our baseline measurement that should include the least amount of digital coupling noise. The remaining 10 measurements were performed with  $10, 20, \ldots, 100$  additional captures (i.e., A/D conversions and frame readouts) within the 24ms integration time, respectively. Digital CDS was performed in each case, using the first and last samples immediately before and after the 24ms integration. Readout speed was set at 1.33GB/s and the total A/D conversion and readout time was  $240\mu$ s per capture. With 100 captures within the 24ms integration, the chip was continuously converting and reading out during the integration period, with no gaps. The entire experiment was repeated twice: once in the dark and once using light from a stabilized light source and an integrating sphere to provide stable, uniform illumination.

The results are plotted in Figure 2.17. It is evident from the data that the noise curves are essentially flat: any trend is insignificant compared to the baseline (with no multi-capture) noise levels.

Figure 2.17: Plot of digital noise coupling results.

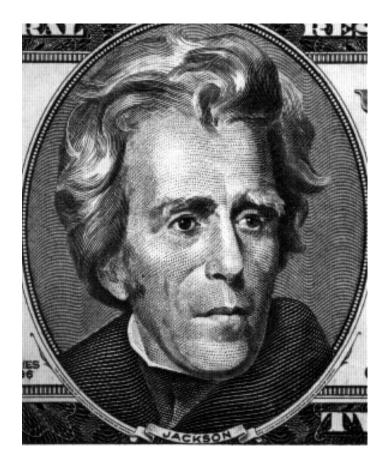

# 2.4.4 Sample images

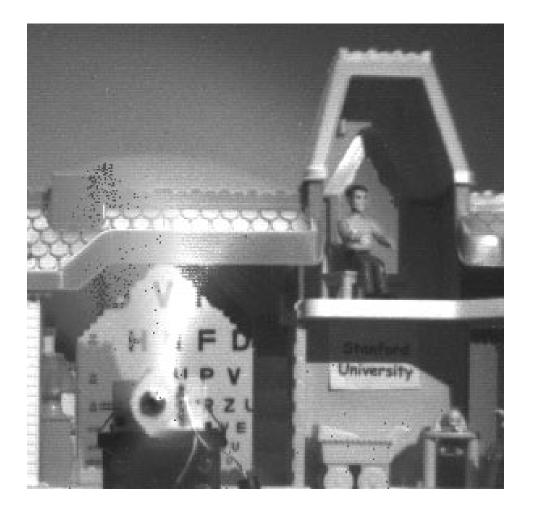

Figure 2.18 shows an image acquired from a 1,000 frames/s (integration time just under 1ms) video stream. Except for digital CDS, no other processing was performed on the image. While the image is of a stationary subject, the chip was operated in continuous video mode. It highlights the image quality that can be obtained at these speeds, even with a small array size and fill factor. Note the subtle aliasing patterns in the finely engraved hair and down-sampling of the background engraving due to the low spatial resolution of the sensor.

Figure 2.18: Sample image.

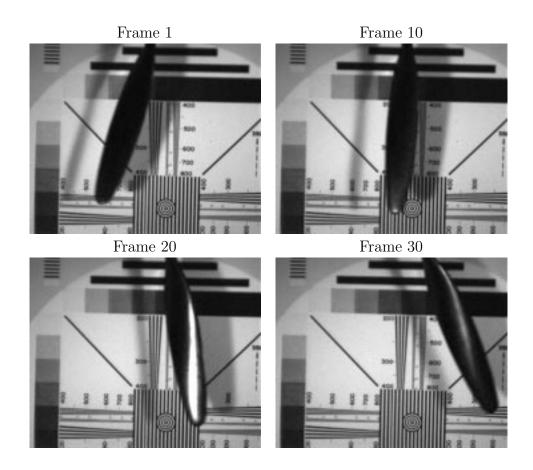

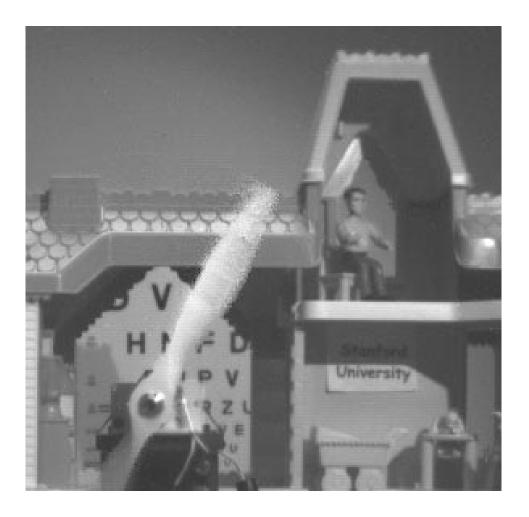

Figure 2.19 shows 4 frames (1, 11, 12 and 31) from a continuous 10,000 frames/s video sequence. They show a model airplane propeller rotating in front of a stationary resolution chart. The propeller is rotating at about 2,200 RPM, which results in each blade rotating by about 40 degrees. The scene is lit from two sides, forming two shadows that follow the propeller. At this speed, neither CDS nor power cycling is used, and each frame's reset and integration is overlapped with the readout of the previous frame's data (mode (D) in Figure 2.10), as explained earlier. The overall image quality appears to be satisfactory for high speed motion analysis and other high speed video applications.

Figure 2.19: 10,000 frames/s image sequence (frames 1, 10, 20, and 30 are shown).

# 2.5 Summary

A Digital Pixel Sensor implemented in a standard digital CMOS  $0.18\mu m$  process was described. The 3.8 million transistor chip has  $352 \times 288$  pixels. Each  $9.4 \times 9.4\mu m$  pixel contains 37 transistors implementing a photogate circuit, an 8-bit single-slope ADC, and 8 3T DRAM cells. Pixel reset, integration and A/D conversion occur in full frame parallel "snap-shot" fashion. Data is read out via a 64 bit wide bus at 167 MHz for a peak data bandwidth of 1.34GB/s. The DPS chip achieved continuous 10,000

frames/s operation and sustained 1 Gpixels/s throughput. With further scaling, significant additional per-pixel memory, processing power and speed will inevitably become practical, further enhancing the capabilities of the DPS approach.

With this test chip, we demonstrated the scalability and high speed potential of DPS. The test chip provides a platform for experimenting with algorithms and circuits that exploit high speed non-destructive readout advantage of CMOS image sensors, as will be described in the following chapters.

# Chapter 3

# Photocurrent Estimation

# Algorithms

Chapter 2 demonstrated the high speed, non-destructive readout capability of CMOS digital pixel image sensor, however, as described in Chapter 1, CMOS image sensors generally suffer from lower SNR and dynamic range than CCDs due to their higher readout noise, and thus higher noise under dark conditions. The high speed non-destructive readout capability of a CMOS image sensor and the ability to integrate memory and signal processing with the sensor on the same chip, open up many possibilities for enhancing its SNR and dynamic range.

Earlier work [80, 102] have demonstrated the use of multiple capture to enhance image sensor dynamic range. The idea is to capture several images at different times within the normal exposure time — shorter exposure time images capture the brighter areas of the scene while longer exposure time images capture the darker areas of the scene. The captured images are then combined into a single high dynamic range image by appropriately scaling each pixel's last sample before saturation. Conventional correlated double sampling (CDS) is used to reduce reset and offset FPN. It was shown that this multiple capture scheme achieves higher SNR than other dynamic

range enhancement schemes [65]. However, this scheme does not take full advantage of the multiple pixel samples. Readout noise, whose power is doubled as a result of performing CDS, remains as high as for conventional sensor operation. As a result, dynamic range is only extended at the high illumination end.

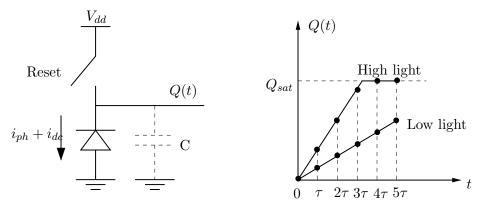

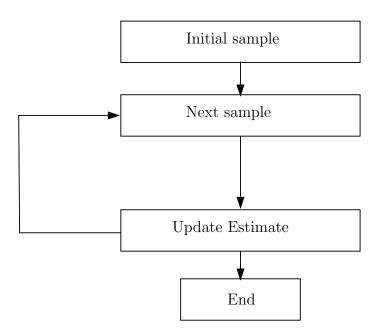

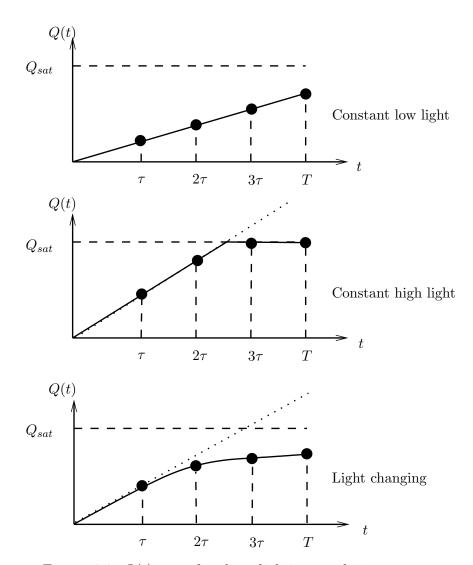

Figure 3.1: Simplified photodiode pixel model and the photocharge Q(t) vs. time t under different light intensity

Figure 3.1 depicts the idea. During capture, each pixel converts incident light into photocurrent  $i_{ph}$ , for  $0 \le t \le T$ , where T is the exposure time. The photocurrent is integrated onto a capacitor and the charge Q(T) (or voltage) is read out at the end of exposure time T. Dark current  $i_{dc}$  and additive noise corrupt the photocharge. The noise can be expressed as the sum of three independent components, (i) shot noise  $U(T) \sim \mathcal{N}(0, q(i_{ph} + i_{dc})T)$ , where q is the electron charge, (ii) readout circuit noise V(T) (including quantization noise) with zero mean and variance  $\sigma_V^2$ , and (iii) reset and FPN noise C with zero mean and variance  $\sigma_C^2$ , which is the same for all multiple captures. Thus the output charge from a pixel can be expressed as

$$Q(T) = \begin{cases} (i_{ph} + i_{dc})T + U(T) + V(T) + C, & \text{for } Q(T) \leq Q_{sat} \\ Q_{sat}, & \text{otherwise} \end{cases}$$

where  $Q_{sat}$  is the saturation charge, also referred to as well capacity. The SNR can

be expressed as

$$SNR(i_{ph}) = 10 \log_{10} \frac{(i_{ph}T)^2}{q(i_{ph} + i_{dc})T + \sigma_V^2 + \sigma_C^2}$$

Note that SNR increases with  $i_{ph}$ , first at 20dB per decade when reset and readout noise dominate, then at 10dB per decade when shot noise dominates. SNR also increases with T. Thus it is always preferred to have the longest possible exposure time. Therefore, [80, 102] use the last sample before saturation with proper scaling as the photocurrent estimate. The justification for ignoring all other samples before saturation is that the last sample has the highest SNR. This is quite acceptable at the high illumination end, where shot noise dominates. However, only using the last sample to estimate the photocurrent is virtually like throwing away the signal and noise information carried in those earlier samples. As will be shown in this chapter, this will result in suboptimal SNR and dynamic range, especially at low illumination condition.

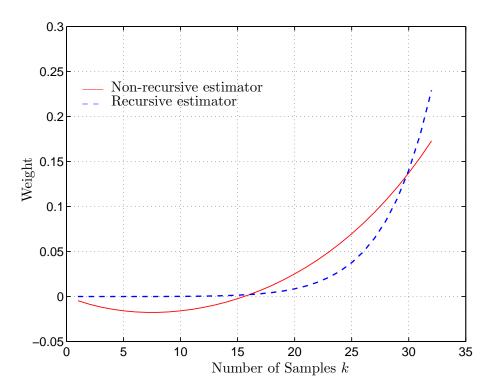

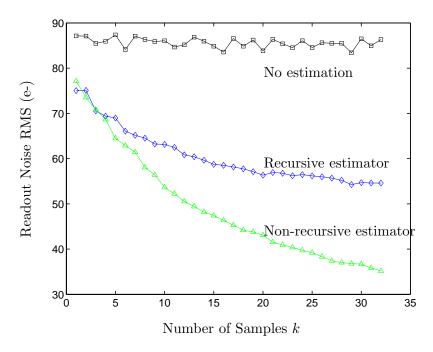

This chapter explores the use of linear mean-square-error estimation to more fully exploit the multiple pixel samples to reduce readout noise and thus extend dynamic range at the low illumination end. We present three estimation algorithms: (1) a recursive estimator when reset noise and offset FPN are ignored, (2) a non-recursive algorithm when reset noise and FPN are considered, and (3) a recursive estimation algorithm for case (2), which achieves mean square error close to the non-recursive algorithm without the need to store all the samples. The later recursive algorithm is attractive since it requires the storage of only a few pixel values per pixel, which makes its implementation in a single chip digital imaging system feasible.

# 3.1 Estimation Algorithms

We assume n+1 pixel charge samples  $Q_k$  captured at times  $0, \tau, 2\tau, \ldots, n\tau = T$  and define the pixel current  $i = i_{ph} + i_{dc}$ . The kth charge sample is thus given by

$$Q_k = ik\tau + \sum_{j=1}^k U_j + V_k + C, \text{ for } 0 \le k \le n,$$

(3.1)

where  $V_k$  is the readout noise of the kth sample,  $U_j$  is the shot noise generated during the time interval  $((j-1)\tau, j\tau]$ , and C is the reset noise. The  $U_j$ s,  $V_k$ , C are independent zero mean random variables with

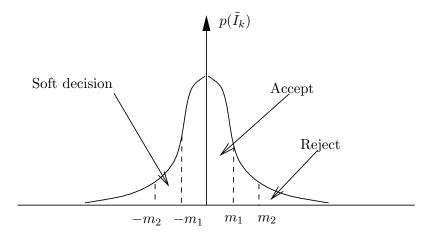

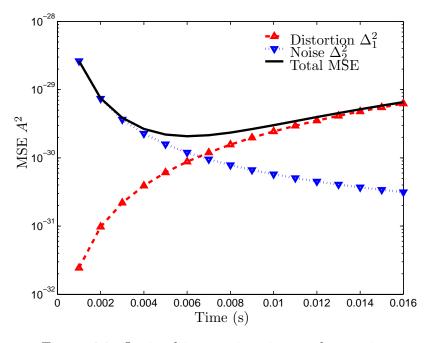

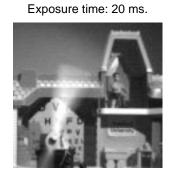

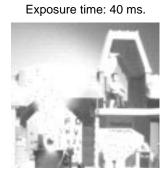

$$\begin{split} E(V_k^2) &= \sigma_V^2 > 0, \text{ for } 0 \leq k \leq n, \\ E(U_j^2) &= \sigma_U^2 = qi\tau, \text{ for } 1 \leq j \leq k, \text{ and } \\ E(C^2) &= \sigma_C^2. \end{split}$$